### **Discontinued Product**

This device is no longer in production. The device should not be purchased for new design applications. Samples are no longer available.

Date of status change: December 5, 2016

Recommended Substitutions: no direct replacement

For existing customer transition, and for new customers or new applications, contact Allegro Marketing.

NOTE: For detailed information on purchasing options, contact your local Allegro field applications engineer or sales representative.

Allegro MicroSystems, LLC reserves the right to make, from time to time, revisions to the anticipated product life cycle plan for a product to accommodate changes in production capabilities, alternative product availabilities, or market demand. The information included herein is believed to be accurate and reliable. However, Allegro MicroSystems, LLC assumes no responsibility for its use; nor for any infringements of patents or other rights of third parties which may result from its use.

### **Features and Benefits**

- Fully integrated current sensor IC in a compact QSOP package eliminates the need for shunt resistors

- Hall effect sensing technology eliminates the error associated with shunt resistor variation due to temperature

- High accuracy: typical error < 2% over operating temperature range

- Fast response digital fault output with programmable level through I<sup>2</sup>C bus interface

- Digital output through I<sup>2</sup>C interface with 9-bit A-to-D conversion for high resolution current measurement

- User-selectable decimation averaging of current output; up to 256 samples

- Freeze pin for holding current measurement value while reading many sensors serially

- User-selectable (via I<sup>2</sup>C) coarse sensitivity and OC fault levels, for exceptional flexibility to meet application requirements

Continued on the next page...

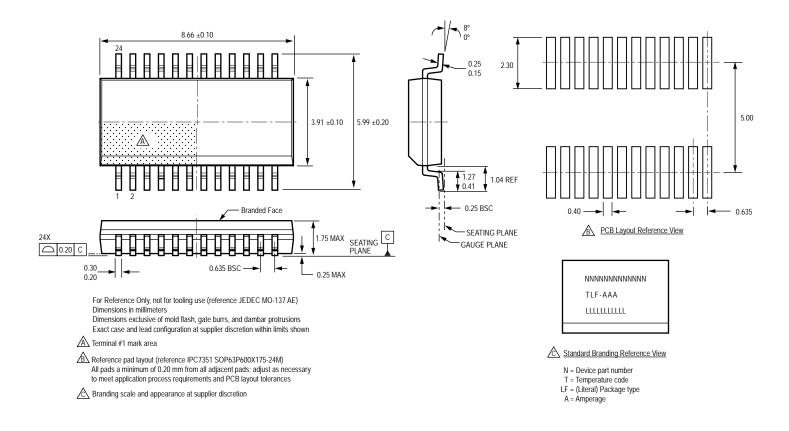

Package: 24-pin QSOP (suffix LF)

Not to scale

### Description

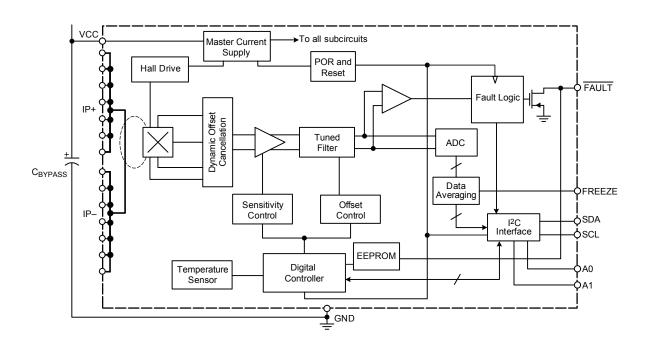

The Allegro<sup>™</sup> ACS764 fully integrated Hall-effect current sensor IC is designed for applications that require digital current sensing and reporting through an I<sup>2</sup>C<sup>™</sup> bus. Allegro factory programming of the offset and gain, including the temperature coefficients, stabilizes the offset and gain over the operating temperature range. This programming greatly reduces the device total error, typically less than 2% over the operating temperature range. A fast response digital fault output is also provided. Both coarse sensitivity and fault level can be programmed via an I<sup>2</sup>C control register, and can be used for enhanced diagnostic functions.

The integrated low resistance conductor eliminates the requirement for external shunt resistors and, by employing Hall-effect sensing technology, eliminates the error associated with changing sense resistance due to temperature. The device allows 16 unique I<sup>2</sup>C bus addresses, selectable via external pins. The sensor IC gain can be selected by the user through the I<sup>2</sup>C bus. The device uses a BiCMOS process that allows a highly stable chopper-stabilized small signal amplifier design.

The ACS764 is provided in a compact 24-pin QSOP package (suffix LF). The leadframe is plated with 100% matte tin, which is compatible with standard lead (Pb) free printed circuit board assembly processes. Internally, the device is Pb-free, except for flip-chip high-temperature Pb-based solder balls, currently exempt from RoHS.

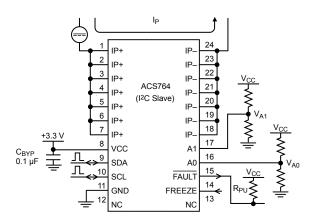

### **Typical Application Diagrams**

### Fully Integrated, Hall-Effect Based Current Sensor IC with I<sup>2</sup>C Digital Output and Low-Resistance Current Conductor

### Features and Benefits (continued)

- Less than  $0.5 \text{ m}\Omega$  series resistance greatly reduces power dissipation and heat generation

- Factory programmed temperature compensation stabilizes sensitivity and offset voltage throughout the operating temperature range

- 16 programmable I<sup>2</sup>C addresses

- Unidirectional DC current sensing and reporting

- Immunity to stray magnetic fields simplifies PCB layout

#### **Selection Guide**

| Part Number        | Packing*                        | Packing*  Operating Ambient Temperature,T <sub>A</sub> (°C) |    | Optimized<br>Nominal Resolution<br>(mA/LSB) |

|--------------------|---------------------------------|-------------------------------------------------------------|----|---------------------------------------------|

| ACS764XLFTR-32AU-T | Tape and reel, 2500 pieces/reel | -20 to 125                                                  | 32 | 62.62                                       |

| ACS764XLFTR-16AU-T | Tape and reel, 2500 pieces/reel | –20 to 125                                                  | 16 | 31.31                                       |

<sup>\*</sup>Contact Allegro<sup>TM</sup> for additional packing options.

#### **Absolute Maximum Ratings**

| Characteristic                                       | Symbol               | Notes               | Rating     | Unit |

|------------------------------------------------------|----------------------|---------------------|------------|------|

| Forward Supply Voltage                               | V <sub>CC</sub>      |                     | 7          | V    |

| Forward FAULT Pin Voltage                            | $V_{FAULT}$          |                     | 24         | V    |

| DC Forward Voltage (A0, A1, FREEZE pins)             | V <sub>FDCx</sub>    |                     | 7          | V    |

| DC Reverse Voltage (VCC, A0, A1, FAULT, FREEZE pins) | $V_{RDCx}$           |                     | -0.5       | V    |

| Operating Ambient Temperature                        | T <sub>A</sub>       | X temperature range | -20 to 125 | °C   |

| Maximum Junction Temperature                         | T <sub>J</sub> (max) |                     | 165        | °C   |

| Storage Temperature                                  | T <sub>stg</sub>     |                     | -65 to 165 | °C   |

#### **Thermal Characteristics**

| Characteristic                          | Symbol          | Test Conditions                                                                                                                                                                           | Value | Unit |

|-----------------------------------------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|

| Steady State Package Thermal Resistance | $R_{\theta JA}$ | Tested with 30 A DC current and based on ACS764 demo board in 1 cu. ft. of still air. Please refer to product FAQs page on Allegro website for detailed information on ACS764 demo board. | 27    | °C/W |

### **Functional Block Diagram**

### **Pin-out Diagram**

#### **Terminal List Table**

| Number   | Name   | Function                                                                               |

|----------|--------|----------------------------------------------------------------------------------------|

| 1 to 7   | IP+    | Primary current path input terminals                                                   |

| 8        | VCC    | Device power supply                                                                    |

| 9        | SDA    | I <sup>2</sup> C control: interface data signal input/output                           |

| 10       | SCL    | I <sup>2</sup> C control: clock signal input/output                                    |

| 11       | GND    | Device ground                                                                          |

| 12,13    | NC     | No internal connection; connect to GND for optimal ESD performance                     |

| 14       | FREEZE | Digital output register freezing control input; pull-up to stop Data register updating |

| 15       | FAULT  | I <sub>P</sub> fault flag output; active low                                           |

| 16       | A0     | I <sup>2</sup> C control: address input 0                                              |

| 17       | A1     | I <sup>2</sup> C control: address input 1                                              |

| 18 to 24 | IP-    | Primary current path output terminals                                                  |

## Fully Integrated, Hall-Effect Based Current Sensor IC with I<sup>2</sup>C Digital Output and Low-Resistance Current Conductor

**OPERATING CHARACTERISTICS**<sup>1</sup> Valid throughout an ambient temperature range of  $-20^{\circ}$ C to  $125^{\circ}$ C,  $C_{BYPASS} = 0.1 \, \mu\text{F}$ ,

$V_{CC}$  = 3.3 V, unless otherwise noted

| Characteristics                                                                           | Symbol                     | Test Conditions                                                                                                           | Min.        | Тур.                                             | Max. | Unit                 |

|-------------------------------------------------------------------------------------------|----------------------------|---------------------------------------------------------------------------------------------------------------------------|-------------|--------------------------------------------------|------|----------------------|

| Electrical Characteristics                                                                | '                          |                                                                                                                           |             |                                                  |      |                      |

| Supply Voltage                                                                            | V <sub>CC</sub>            |                                                                                                                           | 3.0         | _                                                | 3.6  | V                    |

| Supply Current                                                                            | I <sub>cc</sub>            | No load on SDA and SCL                                                                                                    | _           | 9                                                | 14   | mA                   |

| Power-On Time                                                                             | t <sub>PO</sub>            | T <sub>A</sub> = 25°C; C <sub>BYPASS</sub> = open                                                                         | _           | 64                                               | _    | μs                   |

| Internal Bandwidth                                                                        | BWi                        | Small signal –3 dB; T <sub>A</sub> = 25°C                                                                                 | _           | 2                                                | _    | kHz                  |

| Leadframe Resistance                                                                      | R <sub>P</sub>             | IP+ to IP– through primary current path                                                                                   | _           | 0.5                                              | _    | mΩ                   |

| Current Sensing Range Selection                                                           | •                          |                                                                                                                           |             |                                                  |      | 1                    |

|                                                                                           |                            | [GAIN_RANGE] = 10b                                                                                                        | _           | 8                                                | _    | Α                    |

| Owner to Constitute Day 222                                                               | 000                        | [GAIN_RANGE] = 11b                                                                                                        | _           | 16                                               | _    | Α                    |

| Current Sensing Range <sup>2,3</sup>                                                      | CSR                        | [GAIN_RANGE] = 00b                                                                                                        | _           | 32                                               | _    | А                    |

|                                                                                           |                            | [GAIN_RANGE] = 01b                                                                                                        | _           | 64                                               | _    | А                    |

|                                                                                           |                            | [GAIN_RANGE] = 10b                                                                                                        | _           | 15.66                                            | _    | mA/LSB               |

|                                                                                           | RES                        | [GAIN_RANGE] = 11b                                                                                                        | _           | 31.31                                            | _    | mA/LSB               |

| Nominal Resolution <sup>3</sup>                                                           |                            | [GAIN_RANGE] = 00b                                                                                                        | _           | 62.62                                            | _    | mA/LSB               |

|                                                                                           |                            | [GAIN_RANGE] = 01b                                                                                                        | _           | 125.24                                           | _    | mA/LSB               |

| Output Signal Characteristics                                                             | '                          |                                                                                                                           |             | '                                                |      |                      |

| A-to-D Conversion Resolution                                                              | Res <sub>ADC</sub>         |                                                                                                                           | _           | 9                                                | _    | bit                  |

| A-to-D Conversion Time                                                                    | t <sub>ADC</sub>           |                                                                                                                           | _           | 375 × N                                          | _    | μs                   |

| Average Quantity of Data Points<br>Included in Moving Average<br>Calculation <sup>4</sup> | N                          | [N7:N0]=[0000 0000] through [1111 1111] represents 1 data point through 256 data points                                   | 1           | -                                                | 256  | data point           |

| Analog Noise                                                                              | I <sub>NOISE(rms)(A)</sub> | T <sub>A</sub> = 25°C                                                                                                     | _           | 15                                               | -    | mA                   |

| Analog Noise Density                                                                      | I <sub>NOISE(den)(A)</sub> | T <sub>A</sub> = 25°C                                                                                                     | _           | 0.27                                             | _    | mA/Hz <sup>1/2</sup> |

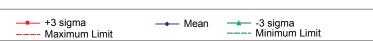

| A-to-D Linear Range <sup>5</sup>                                                          | ADC <sub>LIN</sub>         |                                                                                                                           | 15          | -                                                | 496  | ADC<br>Code          |

| Digital Noise                                                                             | I <sub>NOISE(rms)(D)</sub> | T <sub>A</sub> = 25°C                                                                                                     | _           | I <sub>NOISE(rms)(A)</sub><br>/ N <sup>1/2</sup> | _    | mA                   |

| Accuracy Performance                                                                      | '                          |                                                                                                                           |             |                                                  |      |                      |

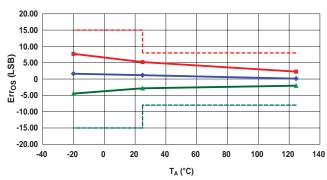

| Offset Error                                                                              |                            | GAIN_RANGE set for optimized CSR, ADC code is within ADC <sub>LIN</sub> ; measured at 2 A; T <sub>A</sub> = 25°C to 125°C | -8          | ±5                                               | +8   | LSB                  |

| Offset Error                                                                              | Err <sub>OS</sub>          | GAIN_RANGE set for optimized CSR; ADC code is within ADC <sub>LIN</sub> ; measured at 2 A; T <sub>A</sub> = -20°C to 25°C | <b>–</b> 15 | ±7                                               | +15  | LSB                  |

Continued on the next page...

## Fully Integrated, Hall-Effect Based Current Sensor IC with I<sup>2</sup>C Digital Output and Low-Resistance Current Conductor

### **OPERATING CHARACTERISTICS<sup>1</sup> (continued)** Valid throughout an ambient temperature range of -20°C to 125°C,

$C_{BYPASS}$  = 0.1  $\mu$ F,  $V_{CC}$  = 3.3 V, unless otherwise noted

| Characteristics                   | Symbol                   | Test Conditions                                                                                                                                  | Min.                | Тур.       | Max.                | Unit |

|-----------------------------------|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------------|---------------------|------|

| Accuracy Performance (continued   | )                        |                                                                                                                                                  |                     |            |                     |      |

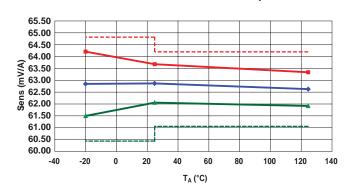

| Desclution Accuracy               | Dec                      | GAIN_RANGE set for optimized CSR,<br>ADC code is within ADC <sub>LIN</sub> ; $T_A$ = 25°C to 125°C;<br>measured at 0.94 × CSR                    | -2.5                | ±1         | +2.5                | %    |

| Resolution Accuracy               | Res <sub>ACC</sub>       | GAIN_RANGE set for optimized CSR,<br>ADC code is within ADC <sub>LIN</sub> ; $T_A = -20^{\circ}$ C to 25°C;<br>measured at 0.94 × CSR            | -3.5                | ±1.5       | +3.5                | %    |

| Nonlinearity Error                | Err <sub>LIN</sub>       | GAIN_RANGE set for optimized CSR, ADC code is within ADC <sub>LIN</sub>                                                                          | _                   | ±0.75      | -                   | %    |

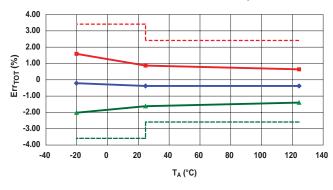

| Total Error                       | Err                      | GAIN_RANGE set for optimized CSR;<br>ADC code is within ADC <sub>LIN</sub> ; Current = $0.94 \times CSR$ ; $T_A = 25^{\circ}C$ to $125^{\circ}C$ | -2.5                | ±1         | +2.5                | %    |

| Total Elloi                       | Err <sub>TOT</sub>       | GAIN_RANGE set for optimized CSR;<br>ADC code is within ADC <sub>LIN</sub> ; Current = $0.94 \times CSR$ ; $T_A = -20^{\circ}C$ to $25^{\circ}C$ | -3.5                | ±2         | +3.5                | %    |

| Lifetime Drift Characteristics    |                          |                                                                                                                                                  |                     |            |                     |      |

| Resolution Lifetime Drift         | Res <sub>DRIFT</sub>     |                                                                                                                                                  | _                   | ±3.0       | _                   | %    |

| Total Error Lifetime Drift        | Err <sub>TOT_DRIFT</sub> |                                                                                                                                                  | _                   | ±3         | _                   | %    |

| Overcurrent Fault Detection Resol | ution/Timing             |                                                                                                                                                  |                     |            |                     |      |

| Fault Current Maximum Setpoint    | I <sub>FAULT(MAX)</sub>  | FAULT_LEVEL = 0000b                                                                                                                              | _                   | 1.46 × CSR | _                   | Α    |

| Fault Current Minimum Setpoint    | I <sub>FAULT(MIN)</sub>  | FAULT_LEVEL = 1111b                                                                                                                              | _                   | 0.5×CSR    | _                   | Α    |

| Digital Fault Level Resolution    | Res <sub>FAULT</sub>     |                                                                                                                                                  | _                   | 4          | -                   | bit  |

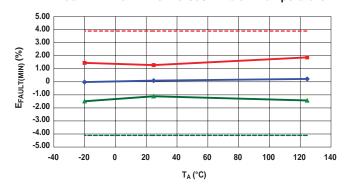

| Fault Level Error <sup>6</sup>    | E <sub>FAULT(MIN)</sub>  | GAIN_RANGE set for optimized CSR; measured at FAULT_LEVEL = 0000b                                                                                | -4                  | ±2.5       | +4                  | %    |

| rault Level Ellois                | E <sub>FAULT(MAX)</sub>  | GAIN_RANGE set for optimized CSR;<br>measured at FAULT_LEVEL = 1111b                                                                             | _                   | ±7         | -                   | %    |

| Pull up Resistance at FAULT Pin   | R <sub>PU</sub>          |                                                                                                                                                  | 10                  | _          | -                   | kΩ   |

| FAULT Output Voltage              | V <sub>FAULT</sub>       | RPU = 10 kΩ, under fault condition                                                                                                               | _                   | -          | 0.4                 | V    |

| Fault Response Time               | t <sub>FAULT</sub>       | Delay from $I_P$ rising above $I_{FAULT}$ until $V_{FAULT} < 0.4 \text{ V}$                                                                      | -                   | 100        | -                   | μs   |

| FREEZE Pin Characteristics        |                          |                                                                                                                                                  |                     |            |                     |      |

| FREEZE Pin Input Level (Low)      | V <sub>FREEZE(IL)</sub>  |                                                                                                                                                  | _                   | _          | 0.2×V <sub>CC</sub> | V    |

| FREEZE Pin Input Level (High)     | V <sub>FREEZE(IH)</sub>  |                                                                                                                                                  | 0.8×V <sub>CC</sub> | _          | _                   | V    |

| FREEZE Pin Input Impedance        | R <sub>FREEZE(IN)</sub>  |                                                                                                                                                  | _                   | 10         | _                   | kΩ   |

Continued on the next page...

5

### Fully Integrated, Hall-Effect Based Current Sensor IC with I<sup>2</sup>C Digital Output and Low-Resistance Current Conductor

### OPERATING CHARACTERISTICS<sup>1</sup> (continued) Valid throughout an ambient temperature range of -20°C to 125°C,

$C_{BYPASS} = 0.1 \mu F$ ,  $V_{CC} = 3.3 \text{ V}$ , unless otherwise noted

| Characteristics                          | Symbol             | Test Conditions | Min.                      | Тур.                      | Max.                      | Unit |

|------------------------------------------|--------------------|-----------------|---------------------------|---------------------------|---------------------------|------|

| Address Pin Characteristics <sup>7</sup> | ·                  |                 |                           |                           |                           |      |

| Address Value 0 Voltage                  | V <sub>ADDR0</sub> | A0, A1 pins     | _                         | 0                         | 0.08 ×<br>V <sub>CC</sub> | V    |

| Address Value 1 Voltage                  | V <sub>ADDR1</sub> | A0, A1 pins     | 0.28 × V <sub>CC</sub>    | 0.31 ×<br>V <sub>CC</sub> | 0.34 ×<br>V <sub>CC</sub> | V    |

| Address Value 2 Voltage                  | V <sub>ADDR2</sub> | A0, A1 pins     | 0.53 ×<br>V <sub>CC</sub> | 0.56 ×<br>V <sub>CC</sub> | 0.59 ×<br>V <sub>CC</sub> | V    |

| Address Value 3 Voltage                  | V <sub>ADDR3</sub> | A0, A1 pins     | 0.8 ×<br>V <sub>CC</sub>  | V <sub>CC</sub>           | _                         | V    |

| Innuit Bing Compant                      | I <sub>A0</sub>    | A0 pin          | _                         | 100                       | _                         | nA   |

| Input Bias Current                       | I <sub>A1</sub>    | A1 pin          | _                         | 100                       | _                         | nA   |

<sup>&</sup>lt;sup>1</sup>All current measurement accuracy specifications listed in this datasheet apply only for the optimized current sensing range.

Allegro MicroSystems, LLC

<sup>&</sup>lt;sup>2</sup>The ACS764 will be most accurate in its optimized gain range.

<sup>3</sup>The GAIN\_RANGE setting of 11b selects the Optimized Nominal Resolution for the 16AU variant, and the GAIN\_RANGE setting of 00b selects the Optimized Nominal Resolution for the 32AU variant.

<sup>&</sup>lt;sup>4</sup>Programmable by user through the I<sup>2</sup>C interface.

<sup>&</sup>lt;sup>5</sup>The ADC is most linear within ADC<sub>LIN</sub>, so code readings outside ADC<sub>LIN</sub> should not be used for precise measurement.

<sup>&</sup>lt;sup>6</sup>Percentage of CSR. See table 3 and Definitions of Accuracy Characteristics section.

<sup>&</sup>lt;sup>7</sup>Address pin characteristics are ensured by designed but are not factory tested.

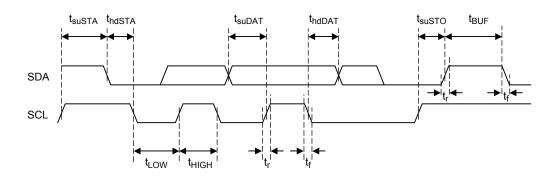

I<sup>2</sup>C INTERFACE CHARACTERISTICS\* Valid at an ambient temperature range of –20°C to 125°C and V<sub>CC</sub> = 3.3 V; unless otherwise noted

| Characteristics                                     | Symbol             | Test Conditions                                    | Min.                | Тур. | Max.                | Unit |

|-----------------------------------------------------|--------------------|----------------------------------------------------|---------------------|------|---------------------|------|

| Bus Free Time Between Stop and Start                | t <sub>BUF</sub>   |                                                    | 1.3                 | _    | _                   | μs   |

| Hold Time Start Condition                           | t <sub>hdSTA</sub> |                                                    | 0.6                 | _    | _                   | μs   |

| Setup Time for Repeated Start Condition             | t <sub>suSTA</sub> |                                                    | 0.6                 | _    | _                   | μs   |

| SCL Low Time                                        | t <sub>LOW</sub>   |                                                    | 1.3                 | -    | -                   | μs   |

| SCL High Time                                       | t <sub>HIGH</sub>  |                                                    | 0.6                 | -    | _                   | μs   |

| Data Setup Time                                     | t <sub>suDAT</sub> |                                                    | 100                 | -    | _                   | ns   |

| Data Hold Time                                      | t <sub>hdDAT</sub> |                                                    | 0                   | -    | 900                 | ns   |

| Setup Time for Stop Condition                       | t <sub>suSTO</sub> |                                                    | 0.6                 | _    | _                   | μs   |

| Logic Input Low Level (SDA, SCL pins)               | V <sub>IL</sub>    |                                                    | -                   | -    | 0.3×V <sub>CC</sub> | V    |

| Logic Input High Level (SDA, SCL pins)              | V <sub>IH</sub>    |                                                    | 0.7×V <sub>CC</sub> | -    | -                   | V    |

| Logic Input Current                                 | I <sub>IN</sub>    | VIN = 0 V to V <sub>CC</sub>                       | -1                  | -    | 1                   | μA   |

| Output Voltage (SDA pin)                            | V <sub>OL</sub>    | $R_{PU} = 1 \text{ k}\Omega, C_B = 100 \text{ pF}$ | -                   | -    | 0.2×V <sub>CC</sub> | V    |

| Logic Input Rise Time (SDA, SCL pins)               | t <sub>r</sub>     |                                                    | -                   | -    | 300                 | ns   |

| Logic Input Fall time (SDA, SCL pins)               | t <sub>f</sub>     |                                                    | -                   | -    | 300                 | ns   |

| SDA Output Rise Time                                | t <sub>r</sub>     | $R_{PU} = 1 \text{ k}\Omega, C_B = 100 \text{ pF}$ | -                   | -    | 300                 | ns   |

| SDA Output Fall Time                                | t <sub>f</sub>     | $R_{PU} = 1 \text{ k}\Omega, C_B = 100 \text{ pF}$ | -                   | -    | 300                 | ns   |

| Clock Frequency (SCL pin)                           | f <sub>CLK</sub>   |                                                    | -                   | -    | 400                 | kHz  |

| SDA and SCL Bus Pull-up Resistor                    | R <sub>PU</sub>    |                                                    | -                   | 1    | -                   | kΩ   |

| Total Capacitive Load for Each of SDA and SCL Buses | C <sub>B</sub>     |                                                    | -                   | -    | 100                 | pF   |

<sup>\*</sup>I<sup>2</sup>C interface characteristics are ensured by designed but are not factory tested.

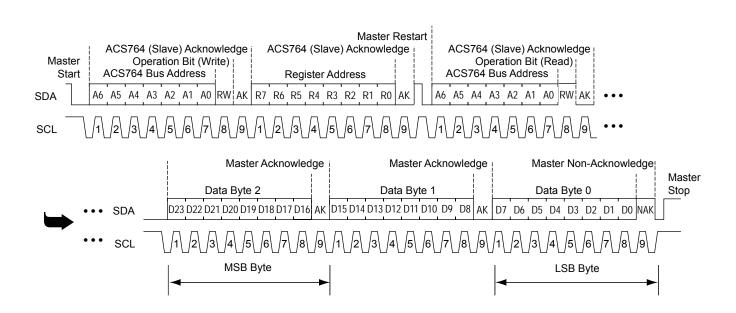

### I<sup>2</sup>C Interface Timing Diagram

### **Application Information**

The ACS764 is a fully integrated Hall-effect based current sensor IC with a digital current output and an overcurrent fault output for current monitoring and reporting applications. The digital output can be read from the ACS764 by a master controller through the I<sup>2</sup>C interface. The I<sup>2</sup>C interface can also be used to control some features of the ACS764. Sixteen device addresses are available through two input pins (A0, A1), allowing multiple devices to be connected to the same I<sup>2</sup>C bus in the application.

The output data that can be read from the ACS764 through the I<sup>2</sup>C interface includes the following:

- Current amplitude (9 bits)

- Unlatched overcurrent fault flag (1 bit)

- Latched overcurrent fault flag (1 bit)

- Unread new current data flag (1 bit)

The control data that can be written to the ACS764 through I<sup>2</sup>C interface includes the following:

- Current range selection (2 bits)

- Overcurrent fault level selection (4 bits)

- Digital averaging filter data point selection (8 bits)

- Latched overcurrent fault flag reset (1 bit)

### I<sup>2</sup>C Interface

I<sup>2</sup>C is a serial interface that uses two bus lines, SCL and SDA, to access the internal device registers. Data is exchanged between a master controller (for example, a microcontroller) and the ACS764 (slave). The clock input to SCL is generated by the master, while the SDA line functions as either an input or an open drain output, depending on the direction of the data transfer. The I<sup>2</sup>C input thresholds depend on the V<sub>CC</sub> voltage of the ACS764.

### **Timing Considerations**

I<sup>2</sup>C communication is composed of several steps in the following sequence:

- 1. Start Condition. Defined by a negative edge on the SDA line, while SCL is high.

- 2. Address Cycle. 7 device (slave) address bits, plus 1 bit to indicate write (0) or read (1), followed by an acknowledge bit.

- 3. Data Cycles. Reading or writing 8 data bits, followed by an acknowledge bit. This cycle can be repeated for multiple bytes of data transfer. If there are multiple registers in a device (for example, EEPROM), the first data byte could be the register address. See the following sections for further information.

- 4. Stop Condition. Defined by a positive edge on the SDA line, while SCL is high.

Except to indicate a Start or Stop condition, SDA must be stable while the clock is high. SDA can only be changed while SCL is

It is possible for the Start or Stop condition to occur at any time during a data transfer. The ACS764 always responds by resetting the data transfer sequence.

The state of the Read/Write bit is set low to indicate a write cycle and set high to indicate a read cycle.

The master monitors for an acknowledge pulse to determine if the slave device is responding to the address byte sent to the ACS764. When the ACS764 decodes the 7-bit address field as a valid address, it responds by pulling SDA low during the ninth clock cycle.

During a data write from the master, the ACS764 pulls SDA low during the clock cycle that follows the data byte, in order to indicate that the data has been successfully received.

After sending either an address byte or a data byte, the master device must release the SDA line before the ninth clock cycle, in order to allow the handshaking to occur.

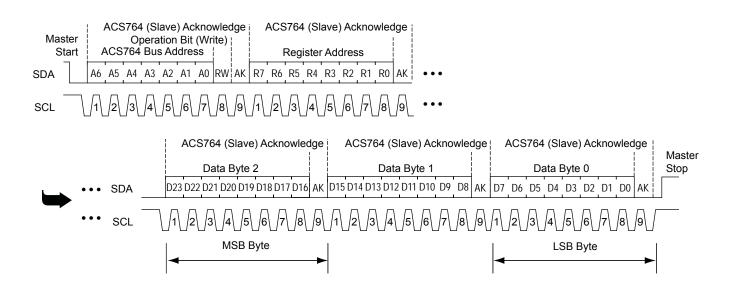

### Writing to ACS764 Registers Through the I<sup>2</sup>C Interface Bus

The master controls the ACS764 by programming it as a slave. To do so, the master transmits data bits to the SDA input of the ACS764 in synchronization with the clocking signal it transmits simultaneously on the SCL input.

A complete transmission begins with the master pulling SDA low (Start bit), and completes with the master releasing the SDA line (Stop bit). Between these points, the master transmits a pattern of slave device (ACS764) address bits with a write command (D0 = 0), and then the target register address (within that device),

and finally the data for the register. Each register in the ACS764 device is three bytes, or 24 bits, long. The address consists of two bytes, comprising: the ACS764 (device) address (7 bits) and the read/write bit, followed by the address byte of the individual register. The data stream of writing data to an individual register is shown in figure 1.

After each byte, the slave ACS764 acknowledges by transmitting

a low to the master on the SDA line. After writing data to a register the master must provide a Stop bit if writing is completed. If the stop bit is not set, then the next three bytes will be written to the current register address + 1. Writing will continue in this fashion until the Stop bit is received. If the total data byte count (that is, not including the Register Address byte) is not modulo three, then the write operation that would contain less than three bytes is not done.

Figure 1. I<sup>2</sup>C interface typical data write to an individual register in the ACS764

### Reading from ACS764 Registers Through the I<sup>2</sup>C Interface Bus

When the master controller performs a data read from an ACS764 internal register, a so-called *combined data transmission* format is used. The I<sup>2</sup>C master provides the Start bit, the ACS764 device (slave) address, the read/write bit set to write (0), and then the initial source register address. The master then issues another Start bit (referred to as *restart*) followed by the same slave address and the read/write bit set to read (1). The ACS764 then provides three bytes of read data, one byte at a time. The data stream of reading

data from an individual register is shown in figure 2.

After each byte of data received, the master acknowledges by transmitting a low to the slave on the SDA line. After receiving three bytes of data from a register, the master must provide a Stop bit if reading is completed. If the Stop bit is not set, then the next three bytes will be read from the initial register address  $\pm$  1. Reading will continue in this fashion until the Stop bit is received. Please note that the acknowledge bit immediately before the Stop bit should be a non-acknowledge (AK = 1).

Figure 2. I<sup>2</sup>C interface typical data read from an individual register in the ACS764

### I<sup>2</sup>C Device (Slave) Address Coding

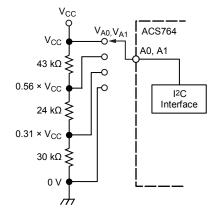

The four LSBs of the device (slave) address (A3, A2, A1, and A0) can be set by applying different voltages to pins A0 and A1 as show in figure 3 and defined in table 1.

Note: Different values for the three MSBs of the address (A6, A5, and A4) are available for factory programming if a conflict with other units occurs in the application design.

### **ACS764 Bus Address Byte Definitions**

| Address Bit                 |    |    |     |     |     |     |  |  |  |

|-----------------------------|----|----|-----|-----|-----|-----|--|--|--|

| A6                          | A5 | A4 | А3  | A2  | A1  | A0  |  |  |  |

| Binary Device Address Value |    |    |     |     |     |     |  |  |  |

| 1                           | 1  | 0  | 0/1 | 0/1 | 0/1 | 0/1 |  |  |  |

Table 1. I<sup>2</sup>C Device Address Coding (Refer to figure 3)

|                                    |                                    | Device A | Address #                 |

|------------------------------------|------------------------------------|----------|---------------------------|

| Voltage on A1 Pin, V <sub>A1</sub> | Voltage on A0 Pin, V <sub>A0</sub> | Decimal  | Binary<br>(A3, A2, A1,A0) |

| 0 V                                | 0 V                                | 0        | 0000                      |

| 0 V                                | 0.31 × V <sub>CC</sub>             | 1        | 0001                      |

| 0 V                                | 0.56 × V <sub>CC</sub>             | 2        | 0010                      |

| 0 V                                | V <sub>CC</sub>                    | 3        | 0011                      |

| 0.31 × V <sub>CC</sub>             | 0 V                                | 4        | 0100                      |

| 0.31 × V <sub>CC</sub>             | 0.31 × V <sub>CC</sub>             | 5        | 0101                      |

| 0.31 × V <sub>CC</sub>             | 0.56 × V <sub>CC</sub>             | 6        | 0110                      |

| 0.31 × V <sub>CC</sub>             | V <sub>CC</sub>                    | 7        | 0111                      |

| 0.56 × V <sub>CC</sub>             | 0 V                                | 8        | 1000                      |

| 0.56 × V <sub>CC</sub>             | 0.31 × V <sub>CC</sub>             | 9        | 1001                      |

| 0.56 × V <sub>CC</sub>             | 0.56 × V <sub>CC</sub>             | 10       | 1010                      |

| 0.56 × V <sub>CC</sub>             | V <sub>CC</sub>                    | 11       | 1011                      |

| V <sub>CC</sub>                    | 0 V                                | 12       | 1100                      |

| V <sub>CC</sub>                    | 0.31 × V <sub>CC</sub>             | 13       | 1101                      |

| V <sub>CC</sub>                    | 0.56 × V <sub>CC</sub>             | 14       | 1110                      |

| V <sub>CC</sub>                    | V <sub>CC</sub>                    | 15       | 1111                      |

Figure 3. External equivalent circuit for I<sup>2</sup>C device address selection

## Fully Integrated, Hall-Effect Based Current Sensor IC with I<sup>2</sup>C Digital Output and Low-Resistance Current Conductor

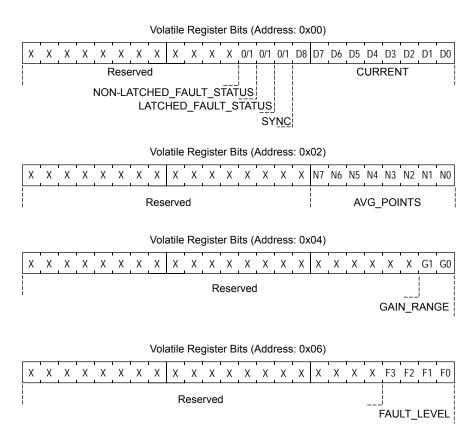

**Table 2. User-Accessible Volatile Memory Registers**

| Data Register                        |       |                          |                                                                    |         |  |  |  |

|--------------------------------------|-------|--------------------------|--------------------------------------------------------------------|---------|--|--|--|

| I <sup>2</sup> C Register<br>Address | Bits  | Parameter Name           | Description                                                        |         |  |  |  |

| 0x00                                 | 23:12 | Reserved                 | Read as all 0s                                                     |         |  |  |  |

| 0x00                                 | 11    | NON-LATCHED_FAULT_STATUS | Non-Latched Fault bit (Read only)                                  |         |  |  |  |

| 0x00                                 | 10    | LATCHED_FAULT_STATUS     | Latched Fault bit; resets with 1 written to this bit (Read/Write)  |         |  |  |  |

| 0x00                                 | 9     | SYNC                     | Sync (new data) bit; resets when this register is read (Read only) |         |  |  |  |

| 0x00                                 | 8:0   | CURRENT                  | Current Sensor output value (digital filter output) (Read only)    |         |  |  |  |

| Control Regis                        | ters  |                          |                                                                    |         |  |  |  |

| I <sup>2</sup> C Register<br>Address | Bits  | Parameter Name           | Description                                                        | Default |  |  |  |

| 0x02                                 | 7:0   | AVG_POINTS               | Number of averaging points (Read/Write)                            | 0       |  |  |  |

| 0x04                                 | 1:0   | GAIN_RANGE               | GAIN_RANGE Current sensing range selection (Read/Write)            |         |  |  |  |

| 0x06                                 | 3:0   | FAULT_LEVEL              | Fault threshold selection (Read/Write)                             | 0       |  |  |  |

### **User-Accessible Register Bit Descriptions**

## Fully Integrated, Hall-Effect Based Current Sensor IC with I<sup>2</sup>C Digital Output and Low-Resistance Current Conductor

### Working with Internal Device Registers Through I<sup>2</sup>C

### **Control Registers**

On power-up the control registers will be loaded to their default values from the EEPROM. The settings can be changed after powering on the device by overwriting the control registers through the I<sup>2</sup>C interface. However, the control registers will revert to their previous levels if the sensor IC is power cycled. Contact your local sales representative if you need the default control register values to be factory-programmed differently.

### **Data Registers**

The volatile register at 0x00 holds all the output data of the device. It includes nine bits of current measurement data and three flag bits: one bit for current output update (SYNC), one bit for latched overcurrent fault (LATCHED FAULT STATUS),

and one bit for non-latched overcurrent fault (NON-LATCHED\_FAULT STATUS), in that order.

After the current measurement data has been updated, SYNC is set. It will be reset when the data is read by a master controller through the I<sup>2</sup>C interface.

When an overcurrent fault condition is detected, both the LATCHED\_FAULT\_STATUS and the NON-LATCHED\_FAULT\_STATUS bits will be set. The NON-LATCHED\_FAULT\_STATUS bit will be reset after the overcurrent condition is removed. However, the LATCHED\_FAULT\_STATUS bit will remain set until a 24-bit word in the format:

XXXX XXXX XXXX X1XX XXXX XXXX

is written to the register.

### **Setting the Overcurrent Fault Threshold**

The Overcurrent Fault threshold,  $I_{\overline{FAULT}}$ , is determined by setting the four FAULT\_LEVEL bits. The combined settings determine the threshold as a percentage of current sensing range, CSR. The  $\overline{FAULT}$  pin will be pulled low when the current is above the programmed I\_FAULT level. The  $\overline{FAULT}$  pin will be released when the current drops below the programmed I\_FAULT level.

The digital NON-LATCHED FAULT STATUS bit will be 1 when the current is above I\_FAULT and 0 when the current is below I\_FAULT. The LATCHED FAULT STATUS bit will be 1 when the current is above I\_FAULT and will only return to being 0 when the current is below I\_FAULT and the bit is reset by writing a 1 to it.

Table 3. I<sup>2</sup>C Control: Settings for Overcurrrent Fault Threshold

|    | FAULT_LE | IFA | ULT |       |                   |

|----|----------|-----|-----|-------|-------------------|

| F3 | F2       | F1  | F0  | Level | Setting<br>(%CSR) |

| 0  | 0        | 0   | 0   | 0     | 50                |

| 0  | 0        | 0   | 1   | 1     | 56                |

| 0  | 0        | 1   | 0   | 2     | 63                |

| 0  | 0        | 1   | 1   | 3     | 69                |

| 0  | 1        | 0   | 0   | 4     | 76                |

| 0  | 1        | 0   | 1   | 5     | 82                |

| 0  | 1        | 1   | 0   | 6     | 88                |

| 0  | 1        | 1   | 1   | 7     | 95                |

| 1  | 0        | 0   | 0   | 8     | 101               |

| 1  | 0        | 0   | 1   | 9     | 108               |

| 1  | 0        | 1   | 0   | 10    | 114               |

| 1  | 0        | 1   | 1   | 11    | 120               |

| 1  | 1        | 0   | 0   | 12    | 127               |

| 1  | 1        | 0   | 1   | 13    | 133               |

| 1  | 1        | 1   | 0   | 14    | 140               |

| 1  | 1        | 1   | 1   | 15    | 146               |

Example: If the required overcurrent fault threshold is 88% of the CSR, then the required FAULT\_LEVEL values are: 0110 (Level 6).

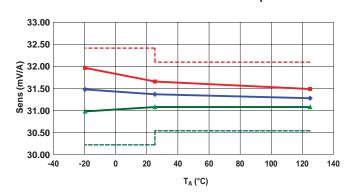

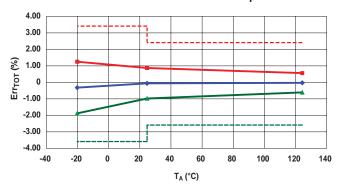

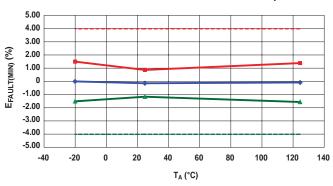

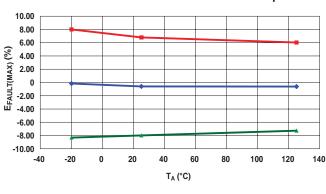

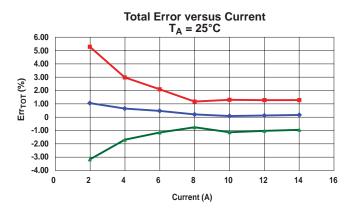

#### **Characteristic Performance Data**

Data taken using the ACS764-32AU

### **Accuracy Data**

#### **Resolution versus Ambient Temperature**

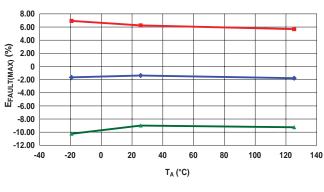

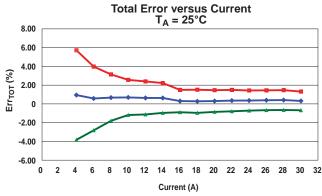

#### **Total Error versus Ambient Temperature**

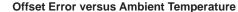

#### Fault Minimum Error versus Ambient Temperature

#### **Fault Maximum Error versus Ambient Temperature**

### **Characteristic Performance Data**

Data taken using the ACS764-16AU

### **Accuracy Data**

#### **Resolution versus Ambient Temperature**

#### **Total Error versus Ambient Temperature**

#### **Fault Minimum Error versus Ambient Temperature**

#### **Fault Maximum Error versus Ambient Temperature**

### **Definitions of Accuracy Characteristics**

### A-to-D Linear Range (ADC<sub>LIN</sub>)

The range of the ADC over which the ADC code is proportional to the current being sensed. One should consider the ADC saturated outside this range. See figure 4.

### Offset Error (Erros)

The offset of the ADC code versus the measured current from the ideal of zero. See figure 4. This parameter is measured at 2 A, as the ADC is below  $ADC_{LIN}$  at zero current. The offset error is calculated as:

$$Err_{OS} = ADC_{CODE}$$

at  $2 A - 2000 \text{ (mA)} \times \frac{1}{RES}$

### Resolution Accuracy (Res<sub>ACC</sub>)

The resolution of the sensor is given in mA/LSB, which is the inverse of the slope of the ADC code versus the measured current (see figure 4). Multiplying the ADC code by the resolution yields the measured current. The Resolution Accuracy (Res<sub>ACC</sub>) is how

Figure 4. A-to-D Linear Range

close the actual resolution is to the Nominal Resolution (RES). The Resolution Accuracy is calculated as:

$$Res_{ACC} = \frac{Measured Resolution - RES}{RES} \times 100 (\%)$$

### Nonlinearity Error (Err<sub>LIN</sub>)

The Nonlinearity Error is a measure of how linear the ADC code versus measured current curve is. The nonlinearity is calculated as:

$$Err_{LIN} = \left\{1 - \frac{0.5}{0.94} \left[ \frac{ADC_{CODE} (0.94 \times CSR) - Err_{OS}}{ADC_{CODE} (0.5 \times CSR) - Err_{OS}} \right] \right\} \times 100 (\%)$$

### Total Error (Err<sub>TOT</sub>)

The percentage difference between the current measurement from the sensor IC and the actual current being measured ( $I_p$ ), relative to the actual current. This is equivalent to the percentage difference between the ideal ADC code and the actual ADC code, relative to the ideal ADC code:

$$Err_{TOT}(I_{P}) = \frac{ADC_{IDEAL}(I_{P}) - ADC(I_{P})}{ADC_{IDEAL}(I_{P})} \times 100 \text{ (\%)}$$

The Total Error incorporates all sources of error and is a function of the measured current ( $I_p$ ). At relatively high currents,  $Err_{TOT}$  will be mostly due to the Resolution Accuracy, and at relatively low currents,  $Err_{TOT}$  will be mostly due to the Offset Error.

### Fault Level Error (E<sub>FAULT(MIN)</sub>, E<sub>FAULT(MAX)</sub>)

The Fault Level Error is a measure of the accuracy of the overcurrent fault function.  $E_{FAULT(MIN)}$  is  $E_{FAULT}$  measured at FAULT\_LEVEL = 0000b, and  $E_{FAULT(MAX)}$  is  $E_{FAULT}$  measured at FAULT\_LEVEL = 1111b. The Fault Level Error is calculated as:

$$E_{\mathrm{FAULT}}(\mathrm{FAULT\_LEVEL}) = \frac{\mathrm{Fault\ Trip\ Current}}{\mathrm{CSR} \times 100\ (\%)} - I_{\mathrm{FAULT\_Percent}}$$

where  $I_{FAULT\_Percent}$  is the ideal percentage of CSR at which the overcurrent fault should trip, based on the FAULT\_LEVEL settings as given in table 3. For example, if FAULT\_LEVEL is set to 0000b, the ideal trip point is at 50% of CSR. An  $E_{FAULT(MIN)}$  specification of  $\pm 4\%$  means the actual trip point ia between 46% and 54% of CSR.

## Fully Integrated, Hall-Effect Based Current Sensor IC with I<sup>2</sup>C Digital Output and Low-Resistance Current Conductor

### **Dynamic Response Characteristics**

### Power-On Time (t<sub>PO</sub>):

When the supply is ramped to its operating voltage, the device requires a finite time to power its internal components before responding to a magnetic field due to current flow through the sensor. Power-On Time,  $t_{\rm PO}$ , is defined as the time it takes from when the supply voltage ( $V_{\rm CC}$ ) reaches its minimum specified voltage to when the value from the ADC is valid, as well as the fault bits and fault output.

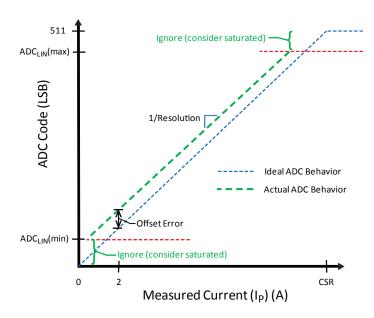

### **Chopper Stabilization Technique**

When using Hall-effect technology, a limiting factor for switchpoint accuracy is the small signal voltage developed across the Hall element. This voltage is disproportionally small relative to the offset that can be produced at the output of the Hall sensor IC. This makes it difficult to process the signal while maintaining an accurate, reliable output over the specified operating temperature and voltage ranges. Chopper stabilization is a unique approach used to minimize Hall offset on the chip. Allegro employs a patented technique to remove key sources of the output drift induced by thermal and mechanical stresses. This offset reduction technique is based on a signal modulation-demodulation process. The undesired offset signal is separated from the magnetic field-induced signal in the frequency domain, through modulation. The subsequent demodulation acts as a modulation process for the offset, causing the magnetic field-induced signal to recover its original spectrum at baseband, while the DC offset becomes a high-frequency signal. The magnetic-sourced signal then can pass through a low-pass

filter, while the modulated DC offset is suppressed. In addition to the removal of the thermal and stress related offset, this novel technique also reduces the amount of thermal noise in the Hall sensor IC while completely removing the modulated residue resulting from the chopper operation. The chopper stabilization technique uses a high-frequency sampling clock. For demodulation process, a sample-and-hold technique is used. This high-frequency operation allows a greater sampling rate, which results in higher accuracy and faster signal-processing capability. This approach desensitizes the chip to the effects of thermal and mechanical stresses, and produces devices that have extremely stable quiescent Hall output voltages and precise recoverability after temperature cycling. This technique is made possible through the use of a BiCMOS process, which allows the use of low-offset, low-noise amplifiers in combination with high-density logic integration and sample-and-hold circuits.

Concept of Chopper Stabilization Technique

### Package LF, 24-Pin QSOP

## Fully Integrated, Hall-Effect Based Current Sensor IC with I<sup>2</sup>C Digital Output and Low-Resistance Current Conductor

Copyright ©2010-2013, Allegro MicroSystems, LLC I<sup>2</sup>C<sup>TM</sup> is a trademark of Philips Semiconductors.

Allegro MicroSystems, LLC reserves the right to make, from time to time, such departures from the detail specifications as may be required to permit improvements in the performance, reliability, or manufacturability of its products. Before placing an order, the user is cautioned to verify that the information being relied upon is current.

Allegro's products are not to be used in any devices or systems, including but not limited to life support devices or systems, in which a failure of Allegro's product can reasonably be expected to cause bodily harm.

The information included herein is believed to be accurate and reliable. However, Allegro MicroSystems, LLC assumes no responsibility for its use; nor for any infringement of patents or other rights of third parties which may result from its use.

For the latest version of this document, visit our website:

www.allegromicro.com